# TECHNISCHE UNIVERSITÄT MÜNCHEN

Lehrstuhl für Rechnertechnik und Rechnerorganisation / Parallelrechnerarchitektur

> Algorithms and Computer Architectures for Evolutionary Bioinformatics

> > Nikolaos Ch. Alachiotis

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

| Vorsitzender:            | Prof. B. Rost (IN)                         |  |

|--------------------------|--------------------------------------------|--|

| Prüfer der Dissertation: | 1. Prof. A. Stamatakis (TUM Junior Fellow) |  |

|                          | 2. Prof. A. Bode (IN)                      |  |

|                          | 3. Prof. A. Dollas (TU Kreta)              |  |

Die Dissertation wurde am ...... bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am ....... angenommen.

# Algorithms and Computer Architectures for Evolutionary Bioinformatics

Nikolaos Ch. Alachiotis

## Abstract

Many algorithms in the field of evolutionary Bioinformatics have excessive computational requirements. This holds not only because of the continuous accumulation of molecular sequence data, which is driven by significant advances in wet-lab sequencing technologies, but it is also due to the high computational demands of the employed kernels.

This dissertation presents new reconfigurable architectures to accelerate parsimony- and likelihood-based phylogenetic tree reconstruction, as well as effective techniques to speed up the execution of a phylogeny-aware alignment kernel on general-purpose graphics processing units. It also introduces a novel technique to conduct efficient phylogenetic tree searches on alignments with missing data. In addition, a highly optimized software implementation for the  $\omega$  statistic, which is used to detect complete selective sweeps in population genetic data using linkage-disequilibrium patterns of single nucleotide polymorphisms in multiple sequence alignments, is described and made available.

## Acknowledgments

Many people have contributed to the success of this work. I am particularly grateful to Dr. Alexandros Stamatakis who has been supporting me since my undergraduate studies, and spent a great effort on supervising my work. I would also like to thank Prof. Dr. Arndt Bode for co-supervising my thesis and Prof. Apostolos Dollas for being part of my PhD committee. I am extremely grateful to all my colleagues in the Exelixis lab (Simon A. Berger, Pavlos Pavlidis, Fernando Izquierdo, Andre J. Aberer, Jiajie Zhang, Solon Pissis, Kassian Kobert, and Tomas Flouris), who offered advice and support when it was needed. Finally, I want to thank my parents and my sister who have been particularly supportive during my time in Germany.

My position was funded under the auspices of the Emmy-Noether program by the German Science Foundation (DFG, STA 860/2).

## Contents

| 1        | Intr | roduction                                    | 1  |

|----------|------|----------------------------------------------|----|

|          | 1.1  | Motivation                                   |    |

|          | 1.2  | Scientific contribution                      |    |

|          | 1.3  | Structure of the thesis                      |    |

| <b>2</b> | Phy  | ylogenetic Tree Inference                    | 7  |

|          | 2.1  | Introduction                                 |    |

|          | 2.2  | Sequence alignment                           |    |

|          |      | 2.2.1 Pairwise alignment                     |    |

|          |      | 2.2.2 Multiple sequence alignment $\ldots$ . |    |

|          | 2.3  | Evolutionary relationships                   |    |

|          |      | 2.3.1 Phylogenetic trees                     |    |

|          |      | 2.3.2 Problem complexity                     |    |

|          | 2.4  | Phylogenetic inference methods               |    |

|          |      | 2.4.1 Maximum parsimony                      |    |

|          |      | 2.4.2 Maximum likelihood                     |    |

|          |      | 2.4.3 Bayesian inference                     |    |

|          | 2.5  | State-of-the-art software tools              |    |

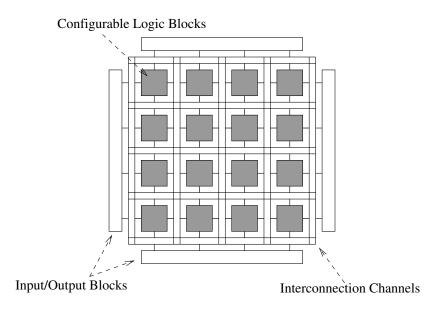

| 3        | FPO  | GA and GPU Architectures                     | 31 |

|          | 3.1  | Introduction                                 |    |

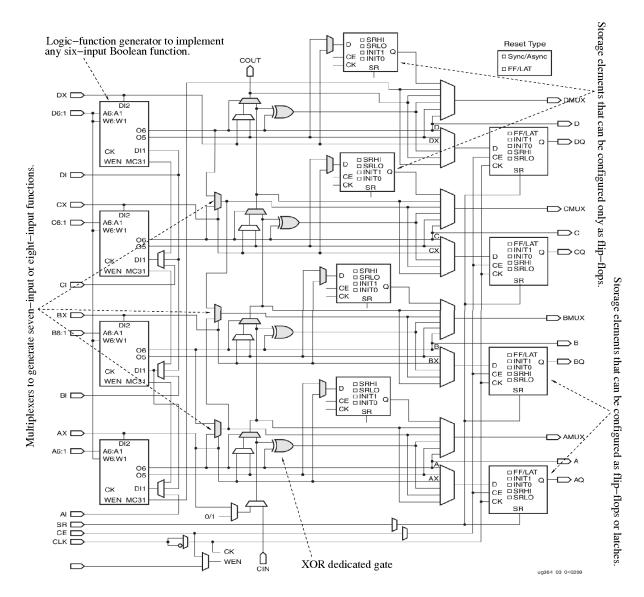

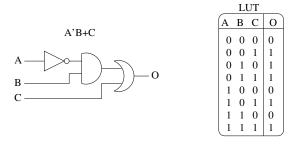

|          | 3.2  | Field-Programmable Gate Array (FPGA)         |    |

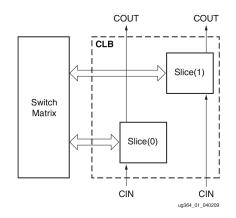

|          |      | 3.2.1 Configurable Logic Block (CLB)         |    |

|          |      | 3.2.2 Specialized blocks and soft IP cores . |    |

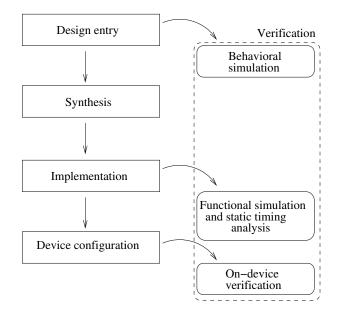

|          |      | 3.2.3 Design flow                            |    |

|          |      | 3.2.4 HDL-based design entry                 |    |

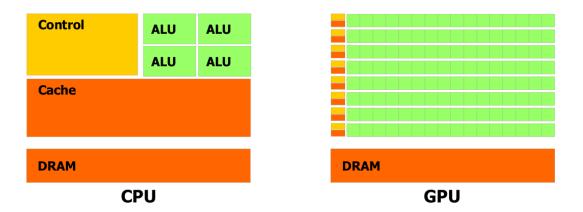

|          | 3.3  | Graphics Processing Unit (GPU)               |    |

|          |      | 3.3.1 Architecture of a GPU                  |    |

|          |      | 3.3.2 OpenCL programming model               |    |

| 4        | Par  | simony Reconfigurable System 45                                                                                                                                  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.1  | Introduction                                                                                                                                                     |

|          | 4.2  | Parsimony kernel                                                                                                                                                 |

|          | 4.3  | Reconfigurable architecture                                                                                                                                      |

|          |      | 4.3.1 Processing unit                                                                                                                                            |

|          |      | 4.3.2 Pipelined datapath                                                                                                                                         |

|          |      | 4.3.3 Population counter                                                                                                                                         |

|          | 4.4  | Implementation $\ldots \ldots \ldots$            |

|          |      | 4.4.1 Verification $\ldots \ldots \ldots$        |

|          |      | 4.4.2 Prototype system                                                                                                                                           |

|          |      | 4.4.3 Performance                                                                                                                                                |

|          | 4.5  | Summary                                                                                                                                                          |

| <b>5</b> | Like | elihood Reconfigurable Architectures 55                                                                                                                          |

|          | 5.1  | Introduction                                                                                                                                                     |

|          | 5.2  | $1^{st}$ generation architecture                                                                                                                                 |

|          |      | 5.2.1 Design $\ldots \ldots 57$                                       |

|          |      | 5.2.2 Operation                                                                                                                                                  |

|          |      | 5.2.3 Experimental setup and results                                                                                                                             |

|          | 5.3  | $2^{nd}$ generation architecture                                                                                                                                 |

|          |      | 5.3.1 Pruning unit                                                                                                                                               |

|          |      | 5.3.2 Pipelined datapath                                                                                                                                         |

|          |      | 5.3.3 Evaluation and performance                                                                                                                                 |

|          | 5.4  | $3^{rd}$ generation architecture                                                                                                                                 |

|          |      | 5.4.1 Co-processor design $\ldots \ldots \ldots$ |

|          |      | 5.4.2 Evaluation and performance                                                                                                                                 |

|          | 5.5  | $4^{th}$ generation architecture                                                                                                                                 |

|          |      | 5.5.1 Likelihood core                                                                                                                                            |

|          |      | 5.5.2 Scaling unit                                                                                                                                               |

|          |      | 5.5.3 Architecture overview                                                                                                                                      |

|          |      | 5.5.4 Host-side management                                                                                                                                       |

|          |      | $5.5.5$ System overview $\ldots$ $81$                                                                                                                            |

|          |      | 5.5.6 Verification and performance                                                                                                                               |

|          | 5.6  | Summary                                                                                                                                                          |

| 6        | Phy  | vlogeny-aware Short Read Alignment Acceleration 85                                                                                                               |

|          | 6.1  | Introduction                                                                                                                                                     |

|          | 6.2  | PArsimony-based Phylogeny-Aware short Read Alignment (PaPaRa) 87                                                                                                 |

|          | 6.3  | Reconfigurable system                                                                                                                                            |

|          |      | 6.3.1 Score Processing Unit (SPU)                                                                                                                                |

|   |      | 6.3.2 Implementation and verification                                                                                                                         |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 6.3.3 System overview                                                                                                                                         |

|   |      | 6.3.4 Performance                                                                                                                                             |

|   | 6.4  | SIMD implementation                                                                                                                                           |

|   |      | 6.4.1 Inter-reference memory organization                                                                                                                     |

|   |      | $6.4.2  \text{Vector intrinsics}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                            |

|   | 6.5  | SIMT implementation                                                                                                                                           |

|   |      | 6.5.1 Inter-task parallelization                                                                                                                              |

|   |      | 6.5.2 Block-based matrix calculation                                                                                                                          |

|   |      | 6.5.3 Loop unrolling $\ldots \ldots \ldots$   |

|   |      | 6.5.4 Data compression $\ldots \ldots \ldots$ |

|   |      | 6.5.5 OpenCL application                                                                                                                                      |

|   |      | 6.5.6 Performance                                                                                                                                             |

|   | 6.6  | Hybrid CPU-GPU approach                                                                                                                                       |

|   |      | 6.6.1 System overview                                                                                                                                         |

|   |      | 6.6.2 Performance                                                                                                                                             |

|   | 6.7  | Summary                                                                                                                                                       |

| 7 | Tree | e Searches on Phylogenomic Alignments with Missing Data 111                                                                                                   |

|   | 7.1  | Introduction                                                                                                                                                  |

|   | 7.2  | Underlying concept                                                                                                                                            |

|   | 7.3  | Static-mesh approach                                                                                                                                          |

|   |      | 7.3.1 Data structure for per-gene meshes                                                                                                                      |

|   |      | 7.3.2 Traversal of a fixed tree                                                                                                                               |

|   | 7.4  | Dynamic-mesh approach                                                                                                                                         |

|   |      | 7.4.1 Subtree pruning                                                                                                                                         |

|   |      | 7.4.2 Subtree regrafting                                                                                                                                      |

|   | 7.5  | Experimental evaluation                                                                                                                                       |

|   |      | 7.5.1 Implementation $\ldots \ldots \ldots$   |

|   |      | 7.5.2 Datasets                                                                                                                                                |

|   |      | 7.5.3 Results                                                                                                                                                 |

|   | 7.6  | Summary                                                                                                                                                       |

| 8 | Sele | ective Sweep Detection in Whole-Genome Datasets 127                                                                                                           |

| C | 8.1  | Introduction                                                                                                                                                  |

|   | 8.2  | Linkage-disequilibrium (LD) pattern of selective sweeps                                                                                                       |

|   | 8.3  | OmegaPlus software   123                                                                                                                                      |

|   | 0.0  | 8.3.1 Computational workflow                                                                                                                                  |

|   |      | 8.3.2 Input/Output                                                                                                                                            |

|   |      | 8.3.3 Memory requirements                                                                                                                                     |

|   |      |                                                                                                                                                               |

## CONTENTS

|    |       | 8.3.4   | Sum of LD values in sub-genomic regions | . 135 |

|----|-------|---------|-----------------------------------------|-------|

|    |       | 8.3.5   | Reuse of LD values                      | . 135 |

|    | 8.4   | Paralle | el implementations                      | . 135 |

|    |       | 8.4.1   | Fine-grain parallelism in OmegaPlus-F   | . 136 |

|    |       | 8.4.2   | Coarse-grain parallelism in OmegaPlus-C | . 136 |

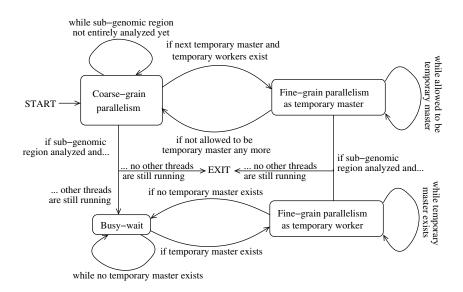

|    |       | 8.4.3   | Multi-grain parallelism in OmegaPlus-M  | . 137 |

|    | 8.5   | Usage   | example                                 | . 139 |

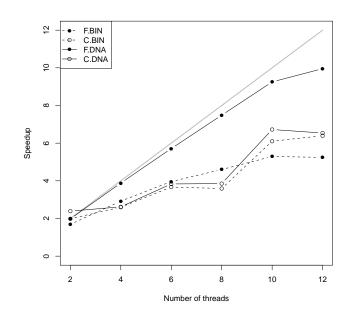

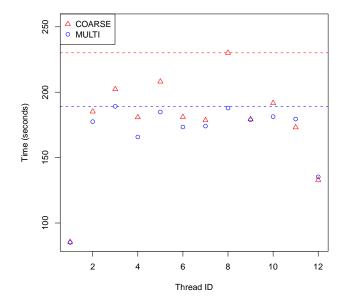

|    | 8.6   | Perfor  | mance evaluation                        | . 140 |

|    | 8.7   | Summ    | ary                                     | . 144 |

| 9  | Con   | clusio  | n and Future Work                       | 147   |

|    | 9.1   | Conclu  | usion                                   | . 147 |

|    | 9.2   | Future  | e work                                  | . 148 |

| Bi | bliog | graphy  |                                         | 150   |

# Chapter 1 Introduction

This introductory chapter provides the motivation for conducting research to improve performance of evolutionary Bioinformatics kernels, summarizes the scientific contribution of this work, and describes the structure of the thesis.

## 1.1 Motivation

Evolution can be seen as the change in the genetic composition of a biological population over time. As a result of the evolutionary process, successive generations appear to have different phenotypic traits such as behavior, morphology, and development. Charles Robert Darwin (1809-1882) was the first to propose a scientific theory of evolution. Darwin established that life on earth originated and evolved from a universal common ancestor 3.7 billion years ago, and explained evolution as the result of a process that he called natural selection. Natural selection takes place in an environment when members of a population that die are replaced by offsprings that are better adapted to survive and reproduce.

The starting point to conduct a genetic analysis of evolution is the genetic material (DNA) of the organisms under investigation. Initially, DNA sequences are extracted from the organisms using sequencing technology. Thereafter, these sequences are aligned using multiple sequence alignment tools and the output of such tools, a multiple sequence alignment (MSA), is then used for further downstream analyses. Phylogenetic studies can be used to determine how a virus spreads over the globe [134] or to describe major shifts in the diversification rates of plants [171]. Population genetics can be used to infer demographic information such as expansion, migration, mutation, and recombination rates in a population, or the location and intensity of selection processes within a genome.

Recent developments in sequencing technologies, such as Next-Generation Sequencing (NGS), have led to an accelerating accumulation of molecular sequence data, since entire genomes can be sequenced quickly, accurately, and more importantly, in a cost-effective way. Several evolutionary Bioinformatics kernels are known to be particularly expensive in terms of computations required. A representative example is the phylogenetic likelihood function (PLF),

which heavily relies on floating-point arithmetics and is used to calculate the likelihood score of phylogenetic tree topologies.

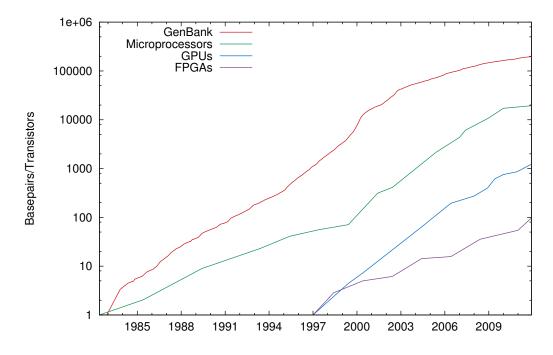

Evidently, Bioinformatics software tools that rely on compute-intensive kernels exhibit long runtimes and usually require excessive computational resources or memory space to execute. Despite the fact that the end of Moore's law has been proclaimed several times in the past decades, the number of transistors that can be placed inexpensively on an integrated circuit still doubles approximately every two years. The current pace of molecular data accumulation is approximately analogous to what Moore's law predicts for modern microprocessor architectures, thus leading to a very slowly decreasing gap—the *bio-gap*—between the increase of available sequence data and microprocessor performance (see Figure 1.1).

Figure 1.1: Growth of molecular data available in GenBank as well as of number of transistors in microprocessors, GPUs, and FPGAs according to Moore's Law.

Fortunately, the computing landscape is experiencing an evolution of its own with the emergence of more powerful processing elements such as Graphics Processing Units (GPUs), Field-Programmable Gate Arrays (FPGAs), and multi-core CPUs. Parallelism, combined with multicore technology, represents the primary approach to increase CPU performance nowadays. As can be observed in the latest Top500 list, High-Performance Computing (HPC) systems are steadily transforming from "classic" supercomputers to large clusters of multi-core processors. Additionally, GPUs and FPGAs are gradually being established as alternatives, since they can serve as co-processors to offload computationally intensive kernels. Certain algorithms witness significant performance improvements (more than one order of magnitude) when ported and

#### 1.2. SCIENTIFIC CONTRIBUTION

executed on such architectures.

Clearly, the immense accumulation of molecular data that needs to be processed and the increased computational demands of the employed kernels in evolutionary Bioinformatics generate a challenge: How to effectively exploit new emerging technologies and/or devise novel algorithmic solutions to accelerate computational kernels, reduce memory requirements, and eventually boost the capacity of modern software tools to keep up with the molecular data growth?

## **1.2** Scientific contribution

This dissertation comprises scientific contributions to the disciplines of phylogenetics and population genetics by introducing novel algorithms and presenting dedicated computer architectures to accelerate widely used kernels and/or reduce their memory requirements.

In computational phylogenetics, commonly used approaches to reconstruct evolutionary trees are maximum parsimony, maximum likelihood, and Bayesian techniques. Maximum parsimony strives to find the phylogenetic tree that explains the evolutionary history of organisms by the least number of mutations. A reconfigurable co-processor to accelerate the parsimony kernel is presented. The FPGA architecture can update ancestral parsimony vectors regardless of the strategy used to search the tree space and calculates final parsimony scores for tree topologies.

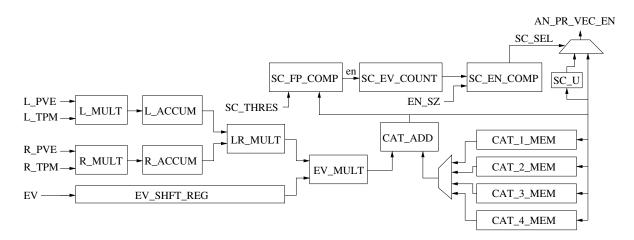

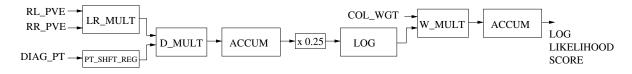

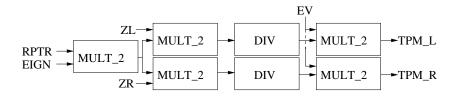

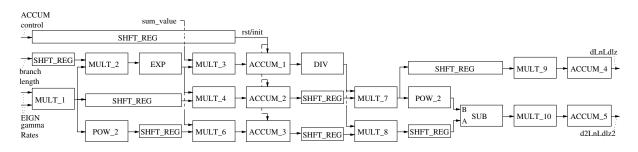

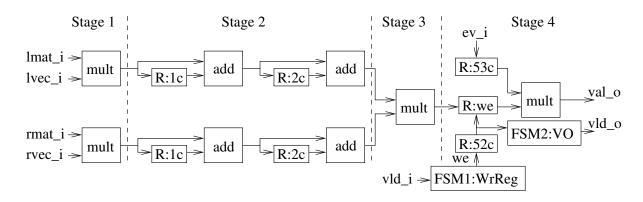

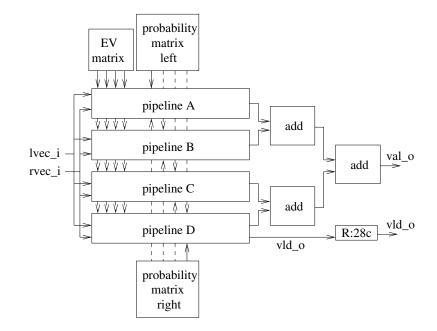

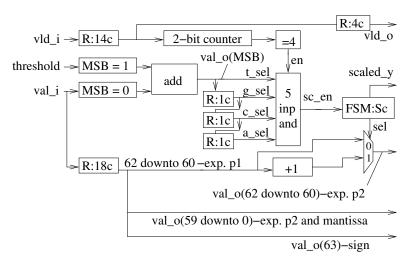

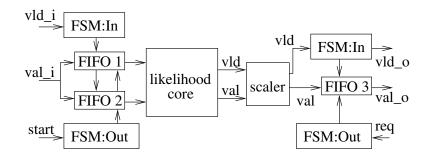

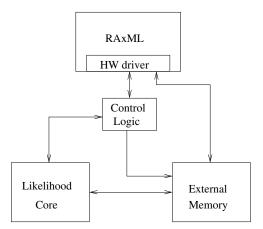

The statistical model of maximum-likelihood estimation in phylogenetics includes the calculation of probabilities for possible tree topologies (evolutionary hypotheses), while Bayesian inference assumes an *a priori* probability distribution of possible trees and employs Markov Chain Monte Carlo sampling algorithms. Both maximum likelihood and Bayesian inference rely on the likelihood function to assess possible tree topologies and explore the tree space. The PLF accounts for approximately 85% to 95% of the total execution time of all likelihood-based phylogenetic tools [182]. Four hardware architectures to compute the PLF are presented. Each design is optimized for a particular purpose. The first two architectures explore different ways to place processing units on reconfigurable logic. In the  $1^{st}$  generation, the processing units are placed in a balanced tree topology, thereby allowing for a deep pipelined datapath and reduced memory requirements. This topology is ideal for fully balanced binary trees. The  $2^{nd}$  generation introduces a vector-like placement of processing units. Such a configuration is generally desirable since performance of the design is independent of the tree topology and search strategy. The  $3^{rd}$  generation is a complete PLF co-processor that comprises dedicated components for all compute-intensive functions of the widely used program RAxML [182]. In addition, it supports all possible input data types: binary, DNA, RNA secondary structure, and protein data. Finally, the  $4^{th}$  generation architecture is a DNA-optimized version of the  $3^{rd}$  generation components for the computation of ancestral probability vectors.

As far as large-scale phylogenomic analyses with hundreds or even thousands of genes are concerned, a property that characterizes the input datasets is that they tend to be gappy. This means that the MSAs contain taxa with many and disparate missing genes. Currently, in phylogenomic analyses there are alignments missing up to 90% of data. A generally applicable mechanism that allows for reducing the memory footprints of likelihood-based phylogenomic analyses in proportion to the amount of missing data in the alignment is presented. Additionally, a set of algorithmic rules to efficiently conduct tree searches via subtree pruning and regrafting moves using this mechanism is introduced and implemented in RAxML.

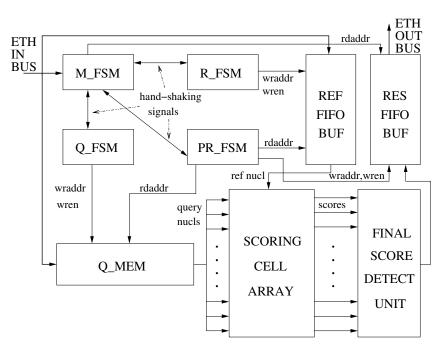

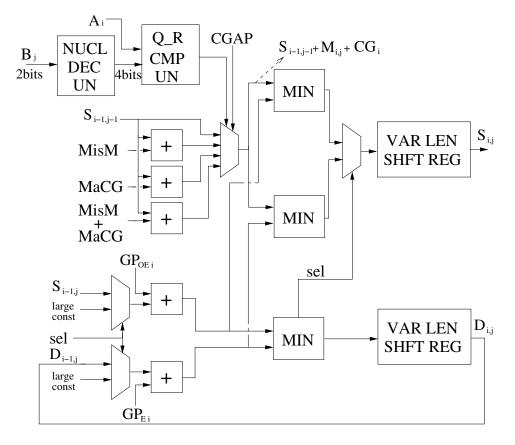

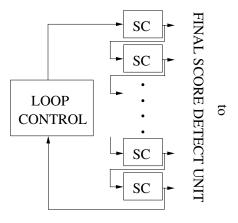

In the context of simultaneous sequence alignment and tree building, novel algorithms have recently been introduced to align short sequence reads to reference alignments and corresponding evolutionary trees. PaPaRa [35] is a dynamic programming algorithm for this purpose. An efficient way to boost performance of sequence alignment programs using hardware accelerators is to offload the alignment kernel (dynamic programming matrix calculations) to the accelerator while maintaining the execution of the trace-back step on the CPU. The alignment kernel of PaPaRa has been accelerated using FPGAs and GPUs. The respective reconfigurable architecture is presented. Also, a series of effective optimizations to port the alignment kernel to SIMT (Single Instruction, Multiple Threads) architectures is described.

In population genetic studies, statistical tests that rely on the selective sweep theory [127] are used to identify targets of recent and strong positive selection by analyzing single nucleotide polymorphisms in intra-species MSAs. A recently introduced method to identify selective sweeps is the  $\omega$  statistic [105]. It uses linkage-disequilibrium (LD) information to capture the non-random association of alleles or states at different alignment positions. Selective sweep theory predicts a pattern of excessive LD in each of the two genomic regions that flank an advantageous and recently fixed mutation. A high-performance approach to compute the  $\omega$  statistic is described. Additionally, a fast technique to calculate sums of LD values in a genomic region based on a dynamic programming algorithm is introduced. OmegaPlus, a software tool that implements these computational advances has been made available under GNU GPL. The tool can rapidly process extremely large datasets without requiring excessive amounts of main memory, therefore allowing for using off-the-shelf computers to carry out whole-genome analyses.

The scientific results of this thesis have been published in seven peer-reviewed conference papers [11, 14, 15, 18, 21, 32, 185]. One more conference paper [13] has been accepted for publication and two journal articles [12, 20] are currently under minor revision. Additionally, three conference papers [10, 16, 19] and a journal article [17] have been published, which describe FPGA cores that were employed in the implementation and/or verification of the reconfigurable architectures. The papers are available for download in PDF format at http://www.exelixis-lab.org/publications.html.

## **1.3** Structure of the thesis

The remainder of this thesis is organized as follows: Chapter 2 introduces the basic concepts and methods for inferring phylogenetic trees from molecular sequence data. Chapter 3 pro-

vides a short introduction to FPGAs, GPUs, and respective programming models. Chapter 4 presents a reconfigurable system for the acceleration of the phylogenetic parsimony kernel. The AVX vectorization (Section 4.4.3) was developed in collaboration with Alexandros Stamatakis. Chapter 5 presents four reconfigurable architectures for computing the phylogenetic likelihood function. The host-side management (Section 5.5.4) was designed and tested in collaboration with Simon A. Berger. Chapter 6 describes the acceleration of a phylogeny-aware short read alignment kernel using reconfigurable hardware, graphics processing units, and vector intrinsics. The SIMD implementation (Section 6.4.2) was developed in collaboration with Simon A. Berger. Chapter 7 introduces an efficient algorithmic approach to search the tree space on phylogenomic alignments with missing genes using maximum likelihood. Chapter 8 introduces the basic concepts of selective sweep detection and presents an optimized software implementation to compute the  $\omega$  statistic on whole-genome datasets. Finally, Chapter 9 provides a conclusion and addresses directions of future work.

## Chapter 2

## **Phylogenetic Tree Inference**

This chapter introduces the basic concepts of sequence alignment and phylogenetic tree inference. Furthermore, it describes the most commonly used alignment algorithms and tree reconstruction methods. Finally, it provides an overview of related state-of-the-art tools.

## 2.1 Introduction

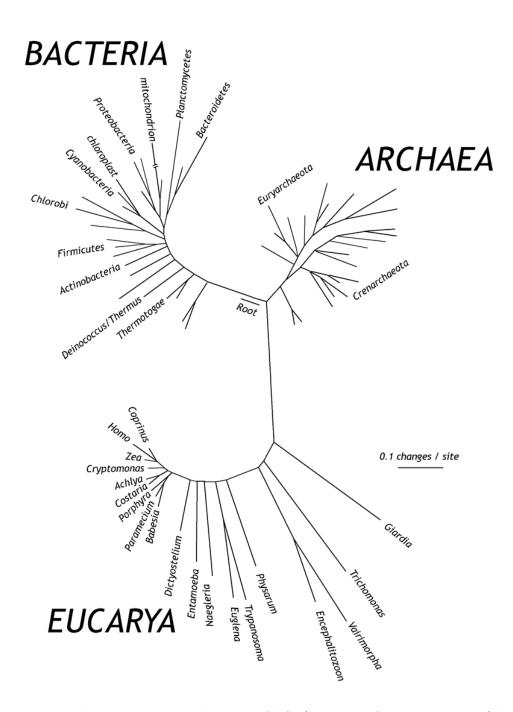

Living organisms inhabit every habitable corner of the Earth, from the poles to the equator, from freezing waters to dry valleys, to several miles in the air, and to groundwater thousands of feet below the Earth's surface. Over the last 3.7 billion years, the living organisms have diversified and adapted to nearly every environment. The Greek philosopher Aristotle (384–322 BC) was the first to carry out a classification of species. He classified all living organisms known at that time as either plants or animals. Today, scientists have identified approximately 2 million species on Earth, which are divided into three groups based on their genetic similarity: Bacteria, Archaea, and Eukarya. These three groups are called domains of life. Figure 2.1 illustrates the three domains of life.

All known organisms today, living and extinct, are connected through descent from a common ancestor. This intuitive connection of organisms is mostly depicted as a bifurcating (binary) tree structure that represents their evolutionary history. Evolutionary trees, also known as phylogenetic trees or phylogenies, clearly show the differences between organisms. Evolutionary relationships among species are derived based upon similarities and differences in their morphological and/or genetic characteristics. The evolutionary history of all life forms on Earth—usually referred to as the Tree of Life—is of interest to scientists for the sake of knowledge. However, small-scale phylogenetic trees that comprise only some groups of species find application in several scientific and industrial fields. D. Bader *et al.* [27] present a list of interesting industrial applications of phylogenetic trees such as in vaccine [83] and drug [42] development or for studying the dynamics of microbial communities [60]. Phylogenies are also used to predict the evolution of infectious diseases [43] or the functions of uncharacterized genes [58]. Forensics [148] is one more field that makes use of phylogenetic trees.

Figure 2.1: Tree showing the three domains of life (Bacteria, Archaea, Eucarya) based on sequencing of 16S ribosomal RNA. (Source: http://www.landcareresearch.co.nz)

#### 2.1. INTRODUCTION

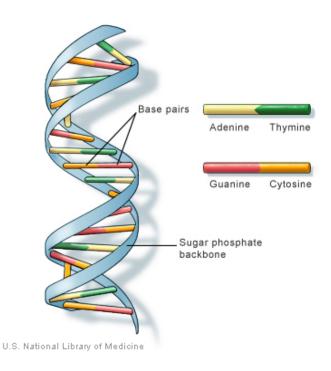

Phylogenetic tree reconstruction is based on the assumption that present-day living organisms are the result of diversification and evolution from ancestral populations or genes. All living organisms can replicate and the replicator molecule is the DNA. DNA (deoxyribonucleic acid) is the genetic material of all known living organisms (apart from RNA viruses). Segments of DNA, which are called genes, carry genetic information used in the development and functioning of the organisms. The information in the DNA is stored as a code consisting of four chemical bases: Adenine (A), Guanine (G), Cytosine (C), and Thymine (T). Each base is attached to a sugar molecule as well as a phosphate molecule, and all together form a nucleotide. Similar to the way letters are placed in a certain order to form words, the information available for building and maintaining an organism is determined by the order of nucleotide bases. DNA is organized into a double helix as shown in Figure 2.2.

Figure 2.2: DNA is a double helix formed by base pairs attached to a sugar-phosphate backbone. (Source: http://ghr.nlm.nih.gov/handbook/basics/dna)

As previously mentioned, DNA sequences are the prerequisite for all genetic analyses. Raw molecular sequence data are produced by DNA sequencing machines that analyze light signals originating from fluorochromes which are attached to nucleotide bases. Sequencing methods determine the order of nucleotide bases in a DNA molecule. The first reliable DNA sequencing attempts date back to the early 1970s when Frederick Sanger developed the chain-termination method. Since then, DNA sequencing has become several orders of magnitude faster and cheaper due to next-generation, high-throughput technologies such as pyrosequencing (http://www.pyrosequencing.com), Illumina (Solexa) sequencing (http://www.illumina.com/technology/solexa\_technology.ilmn), DNA nanoball sequencing (http://www.completegenomics.com) and others. Nowadays, sequencing machines generate millions of DNA sequences that can be some hundreds of bases long depending on the technology. To proceed with downstream analyses, a multiple sequence alignment (MSA) is required, that is, a sequence alignment of three or more biological sequences (protein, DNA, or RNA) which share a lineage (common evolutionary history). This MSA can then be used in phylogenetic analyses to infer the evolutionary history of the sequences.

## 2.2 Sequence alignment

Sequence alignments of DNA or protein data represent the usual starting point for phylogeny reconstruction. Higher-level information, like the order of genes in the genome, can also be used. Note however that gene order phylogenetic inference [131] is more computationally intensive than alignment-based inference and, therefore, less suitable to accommodate today's molecular data flood. Sequence alignment algorithms aim to identify regions of similarity that may be a consequence of functional, structural, or evolutionary relationships between the sequences [133]. In phylogenetic studies, the quality of the final result can only be as good as the quality of the alignment. Thus, a "good" alignment of sequences is the most important prerequisite to conduct a phylogenetic analysis [180].

Alignment approaches are divided into two categories based on the optimization criterion: global optimization or local optimization. Global optimization approaches align two sequences forcing the alignment to span the entire length of the sequences. Local alignment algorithms on the other hand search for subsequences of high similarity. The result is an alignment of only those parts of the sequences that match well. In the following, we provide a brief description of the most popular algorithms and tools for pairwise and multiple sequence alignment.

#### 2.2.1 Pairwise alignment

Pairwise alignment algorithms are used to compute the local or global alignment of only two sequences. There are three primary computational approaches to produce pairwise alignments: dot-matrix, dynamic programming, and word methods [133]. The most known pairwise alignment algorithms are the Needleman-Wunch algorithm [135] for producing global alignments and the Smith-Waterman algorithm [175] for producing local alignments. The Needleman-Wunch algorithm was published in 1970 by Saul B. Needleman and Christian D. Wunsch. It was the first application of dynamic programming to biological sequence comparison. In 1981, Temple F. Smith and Michael S. Waterman proposed the Smith-Waterman algorithm, a variation of the Needleman-Wunch algorithm to find the optimal local alignment of two sequences given a scoring system. Both algorithms exhibit computational similarities since they rely on dynamic programming. For this reason, only an example for the Smith-Waterman algorithm is given here.

To compare two sequences  $A = (a_1 a_2 a_3 \dots a_n)$  and  $B = (b_1 b_2 b_3 \dots b_m)$ , the Smith-Waterman algorithm initializes the first row and column of the dynamic programming matrix with zeros:

$$H_{i,0} = 0, 0 \le i \le n$$

$H_{0,j} = 0, 0 \le j \le m$

and uses pairwise comparisons between individual characters to fill the rest of the matrix as follows:

$$H_{i,j} = max \begin{cases} H_{i-1,j-1} + s(a_i, b_j) & Match/Mismatch \\ H_{i-1,j} + s(a_i, -) & Deletion \\ H_{i,j-1} + s(-, b_j) & Insertion \\ 0 & 0 \end{cases} \qquad 1 \le i \le n, 1 \le j \le m, (2.1)$$

where s is the scoring function: if  $a_i = b_j$  then  $s(a_i, b_j) = s(match)$ , if  $a_i \neq b_j$  then  $s(a_i, b_j) = s(mismatch)$ , and  $s(a_i, -) = s(-, b_j) = s(gap)$  is the gap penalty. To construct the local alignment from the matrix, the starting point for tracing back the path is the highest-scoring matrix cell. The trace-back continues until a cell with zero score is found. Each matrix cell score represents the maximum possible score for all alignments that end at the coordinates of the cell. Thus, starting from the cell with the highest score in the matrix yields the optimal local alignment. For example, one can consider the sequences  $S_1 = ACCCTTGCT$  and  $S_2 = CTGACTT$  as well as a scoring function: s(match) = 1, s(mismatch) = -1, and s(gap) = -2. The scoring matrix is computed as shown in Figure 2.3. The trace-back step starts with the highest value in the matrix and yields the following optimal local alignment:

### A A C C C T T - A - - C T T.

There exist improved variants of the Smith-Waterman algorithm that allow for better accuracy [25] and reduced complexity [77]. Furthermore, there exists extensive literature on accelerating the algorithm using SIMD (Single Instruction, Multiple Data) instructions on general purpose CPUs, GPUs, and hardware description languages on FPGAs. Chapter 6 provides a brief overview of these high-performance implementations.

Despite the fact that the Smith-Waterman algorithm finds the optimal local alignment via a full alignment procedure, the required dynamic programming approach does not allow to search huge databases of sequences within an acceptable amount of time. To this end, BLAST was introduced in 1990 [26]. BLAST stands for Basic Local Alignment Search Tool and represents a heuristic approximation of the Smith-Waterman algorithm. BLAST compares a query sequence

|   |   | А  | A  | C          | C            | C  | Т          | Т | G | C | T |

|---|---|----|----|------------|--------------|----|------------|---|---|---|---|

|   | 0 | 0  | 0  | 0          | 0            | 0  | 0          | 0 | 0 | 0 | 0 |

| С | 0 | 0  | 0  | 1          | 1            | 1  | 0          | 0 | 0 | 1 | 0 |

| Т | 0 | 0  | 0  | 0          | 0            | 0  | 2          | 1 | 0 | 0 | 2 |

| G | 0 | 0  | 0  | 0          | 0            | 0  | 0          | 1 | 2 | 0 | 0 |

| Α | 0 | 1- | -1 | 0          | 0            | 0  | 0          | 0 | 0 | 1 | 0 |

| С | 0 | 0  | 0  | <u></u> 2- | <b>-</b> 1 - | -1 | 0          | 0 | 0 | 1 | 0 |

| Т | 0 | 0  | 0  | 0          | 1            | 0  | <b>^</b> 2 | 1 | 0 | 0 | 2 |

| Т | 0 | 0  | 0  | 0          | 0            | 0  | 1          | 3 | 1 | 0 | 0 |

Figure 2.3: Dynamic programming matrix of the Smith-Waterman algorithm.

with a library of sequences and identifies those sequences in the library that have a higher similarity score than a given threshold. It does not compare two sequences entirely but locates initial word matches (seeds) between the sequences and calculates local alignments afterwards. Evidently, BLAST does not guarantee to find the optimal local alignment, but its relatively good accuracy in combination with reduced execution times has established BLAST as the natural choice for huge genome database searches.

### 2.2.2 Multiple sequence alignment

Multiple sequence alignment (MSA) tackles the problem of aligning three or more sequences. Several computational approaches for generating MSAs exist, e.g., progressive alignment algorithms [142, 198], iterative methods [78], hidden Markov models [94], or genetic algorithms [141]. Constructing MSAs includes two major challenges: i) which scoring function to use and ii) how to find the optimal alignment given a scoring function. Dynamic programming algorithms can be used to align small numbers of homologous sequences [119]. For an alignment of n sequences for instance, the construction of a n-dimensional dynamic programming matrix is required. Clearly, such approach becomes extremely compute- and memory-intensive for large numbers of sequences since the search space increases exponentially with n. Heuristic approaches are deployed to make the alignment of many sequences computationally feasible. The underlying idea of heuristic methods is to determine pairwise alignments of closely related sequences and progressively add other, less related sequences to the alignment. Finding the optimal MSA is a NP-complete problem under most reasonable scoring functions [201].

A variety of MSA algorithms exist, but the problem of MSA construction is beyond the scope of this thesis and, therefore, only the most commonly used algorithms are briefly mentioned. The ClustalW [198] and T-Coffee [142] alignment tools are based on the progressive method. MUSCLE [54] implements an iterative approach and improves upon accuracy as well as speed compared to ClustalW and T-Coffee. MAFFT [102, 103], which implements a progressive method as well as an iterative refinement procedure, outperforms ClustalW and T-Coffee in terms of speed while exhibiting comparable accuracy. FSA (Fast Statistical Alignment [38]) is based on pair hidden Markov models to approximate an insertion/deletion process on a tree and employs a sequence annealing algorithm to combine the posterior probabilities estimated from these models into a multiple sequence alignment. BAli-Phy [159, 193] is a Bayesian posterior sampler that employs Markov chain Monte Carlo to simultaneously estimate multiple sequence alignments and the phylogenetic trees that relate the sequences. Another tool for joint multiple sequence alignment and tree reconstruction is POY [203]. Detailed reviews of state-of-the-art MSA software tools as well as benchmarking can be found in [55] and [197].

## 2.3 Evolutionary relationships

Biological diversity can be classified by assessing degrees of apparent similarity and difference among organisms. Classification of organisms based on observable morphological traits assumes that the biological relationship between organisms is closer the greater the degree of physical similarity is. Nowadays, a generally accepted scientific approach to classify organisms is based on shared evolutionary history. The evolutionary relationships of a group of organisms that share an evolutionary history are depicted by phylogenetic trees.

### 2.3.1 Phylogenetic trees

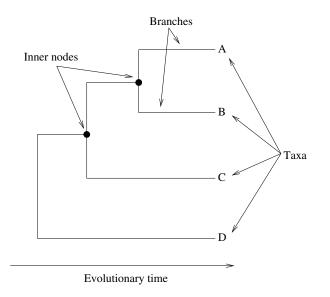

Figure 2.4: A generic phylogenetic tree.

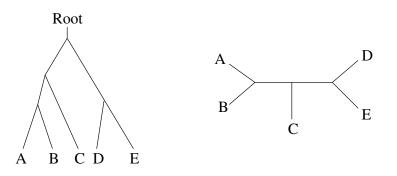

Phylogenetic trees are a graphical way to represent evolutionary relationships. A phylogenetic tree is a tree diagram that consists of leaves (tip nodes) and inner nodes. The tip nodes correspond to individual organisms, species, or sets of species. The items represented by the tip nodes are usually referred to as taxa. The inner nodes (i.e., the branching points within a tree) represent ancestral species. Each inner node corresponds to the most recent common (hypothetical) ancestor of the lineages that descend from that node. The branches of a phylogenetic tree (i.e., the lines that connect all tips and inner nodes) represent the path that traces back the evolutionary history of the lineages. Figure 2.4 shows a generic phylogenetic tree.

Phylogenetic trees can be rooted or unrooted. The root represents the common ancestor of all entities at the leaves of the tree and indicates the direction of the evolutionary process. The term "sister group" is used to describe closely related taxa in rooted trees. Taxa in a sister group share a recent common ancestor, i.e., the inner node that joins them together. Unrooted trees illustrate the relatedness of the entities at the leaves without providing any further information about ancestral relationships. While rooted trees can be trivially transformed into unrooted trees by simply omitting the root, to generate rooted trees based on unrooted ones usually requires the use of an outgroup. An outgroup is a lineage that is known to be more distantly related to all organisms at the tips. Figure 2.5 shows examples of a rooted and an unrooted tree with five taxa. Trees can be either bifurcating or multifurcating. Every inner node in a bifurcating tree has exactly three neighbors (binary tree topology), whereas multifurcating trees allow for more than three neighbors per inner node.

Figure 2.5: A rooted (left) and an unrooted (right) phylogenetic tree with five taxa.

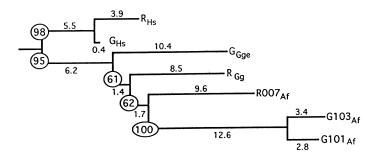

A classification of ogranisms in phylogenetic trees according to the information at the tips leads to two types of trees: species trees and gene trees. Species trees depict evolutionary relationships between species or populations of species. Figure 2.6 illustrates a species tree that shows the divergence of human and ape species. A gene tree (Figure 2.7) on the other hand, is a tree of a group of orthologous genes, each sampled from a different species [136, 196]. Two genes are orthologous if they diverged after a speciation event, i.e., a lineage-splitting event that produces two or more separate species. The outcome of a phylogenetic analysis is a gene tree and does not necessarily represent the actual evolutionary history of the species (species

Figure 2.6: A species tree showing the divergence of human and ape species. Approximate dates of divergence are given for, from left to right, orangutan, gorilla, human, bonobo and chimpanzee. (Source: [150])

Figure 2.7: Phylogenetic tree of visual pigment genes. R: red-sensitive pigment; G: greensensitive pigment. Subscripts as follows: Hs-humans; Gg-chickens; Gge-gecko; Af-fish. (Source: [213])

tree), although ideally these two trees should be identical. Several studies [136, 152, 169] have evaluated the probability that the topology of the gene tree is the same as that of the species tree for various cases such as number of species, number of alleles, or sampling errors with respect to the number of nucleotides.

### 2.3.2 Problem complexity

Phylogenetic tree reconstruction faces a major computational issue: the number of potential alternative tree topologies that need to be evaluated grows super-exponentially with the number of species. For n species for instance, the number of rooted and unrooted binary tree topologies is given as follows [56]:

Rooted trees =

$$\frac{(2n-3)!}{2^{n-2}(n-2)!}$$

$2 \le n$  (2.2)

Unrooted trees =

$$\frac{(2n-5)!}{2^{n-3}(n-3)!}$$

$3 \le n.$  (2.3)

Table 2.1 shows the number of different tree topologies with and without root for up to 100 species. Note that, for a number of species as low as 52, the number of different tree topologies (either rooted or unrooted) is close to the estimated number of atoms in the universe ( $\approx 10^{80}$ ). Thus, it becomes evident that, regardless of the scoring method used to evaluate a tree topology, it is not feasible to evaluate all possible topologies, even for small numbers of species. As a matter of fact, it has been shown that maximum likelihood [46] and maximum parsimony [50]

| Species | Rooted trees      | Unrooted trees    |

|---------|-------------------|-------------------|

| 3       | 3                 | 1                 |

| 4       | 15                | 3                 |

| 5       | 105               | 15                |

| 6       | 945               | 105               |

| 7       | 10,395            | 945               |

| 8       | $135,\!135$       | $10,\!395$        |

| 9       | 2,027,025         | $135,\!135$       |

| 10      | 34,459,425        | $2,\!027,\!025$   |

| 15      | $2.13 * 10^{14}$  | $7.90 * 10^{12}$  |

| 20      | $8.20 * 10^{21}$  | $2.21 * 10^{20}$  |

| 25      | $1.19 * 10^{30}$  | $2.53 * 10^{28}$  |

| 50      | $2.75 * 10^{76}$  | $2.83 * 10^{74}$  |

| 75      | $4.09 * 10^{128}$ | $2.78 * 10^{126}$ |

| 100     | $3.34 * 10^{184}$ | $1.70 * 10^{182}$ |

Table 2.1: Number of possible rooted and unrooted trees with 3–100 organisms. (Computed using TreeCounter [179])

#### 2.4. PHYLOGENETIC INFERENCE METHODS

methods, which both are commonly used in practice, are NP-hard problems. This is the reason that heuristic approaches are deployed in order to search the tree space as efficiently as possible to find the best possible, yet suboptimal topology given a scoring criterion. Furthermore, it has been demonstrated [80, 205] that, while fast scoring methods allow for a more exhaustive search of the tree space, more elaborate scoring functions such as maximum likelihood lead to the detection of better trees. Thus, there is an apparent trade-off between the execution time of an analysis and the quality of the outcome.

## 2.4 Phylogenetic inference methods

There exist two main classes of phylogeny reconstruction methods: distance-matrix methods and character-based methods. Distance-matrix methods, such as UPGMA [176] (Unweighted Pair-Group Method with Arithmetic Mean) or neighbor joining [168], reconstruct a phylogeny of n species by computing a  $n \times n$  distance matrix which contains all pairwise distances between the n sequences. Character-based methods on the other hand, such as maximum parsimony [68] and maximum likelihood [65], use the input MSA to compute tree scores on a column-by-column basis. Distance-matrix methods are much faster but also less accurate than character-based methods, which explains why they are mostly deployed to obtain initial estimates of phylogenetic trees.

The accuracy of phylogenetic inference methods is usually assessed using simulated data. Typically, a tree (true tree) and an evolutionary model are used to simulate sequences. These simulated sequences are then provided as input to phylogenetic tools to infer trees. The accuracy of the employed methods is assessed by examining the topological distance of the inferred trees from the true tree. Although distance-matrix methods represent the only computationally feasible approach to reconstruct very large phylogenies, several studies have revealed that character-based methods usually recover a tree that is topologically closer to the true tree [92, 110, 166]. This section provides a brief description of the most commonly used character-based methods.

### 2.4.1 Maximum parsimony

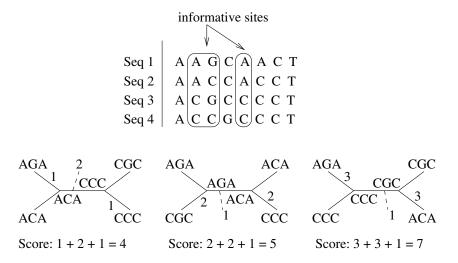

Maximum parsimony (MP) strives to find the phylogenetic tree that explains the evolutionary history of a set of organisms by the least amount of evolutionary changes. Thus, the most parsimonious tree is considered the one that has been obtained with the least number of mutations. Since the parsimony criterion is a character-based method, it operates on the input MSA on a column-by-column basis. Note however that not all columns (sites) in the MSA are informative. Informative sites are those that consist of at least two different character states, and each of these states must occur in more than one sequences. Figure 2.8 shows an example of an MSA with four sequences. Only three out of the eight sites in the MSA are informative and can, therefore, be used in the analysis. Parsimony-uninformative sites are excluded from the analysis because they have the same score regardless of the tree topology. Figure 2.8 also depicts the three unrooted tree topologies for the given number of sequences and shows the parsimony scores.

Figure 2.8: Calculation of parsimony scores for the alternative unrooted tree topologies based on the parsimony informative sites of the 4-sequence MSA and an arbitrary rooting.

MP is not statistically consistent due to the phenomenon of long branch attraction (LBA) [64, 90]. Given an infinite amount of input data, there is no guarantee that MP will recover the true tree. LBA can be observed when very long branches are inferred to be closely related though they have evolved from very different lineages. Similarity between sequences on long branches may be explained by independent multiple substitutions/mutations of the same nucleotide and not by their close relationship. Joe Felsenstein [64] showed the statistical inconsistency of the parsimony criterion in 1978, and this is the reason that the situation in which this inconsistency occurs is also called the "Felsenstein zone".

#### 2.4.2 Maximum likelihood

Maximum likelihood (ML) is a statistical method to fit a mathematical model to the data at hand. According to the likelihood principle, the preferred tree topology is the one that maximizes the probability of observing the data, i.e., the input MSA. The first application of ML in phylogenetic tree reconstruction dates back to 1964 and is due to A.W.F. Edwards and L.L. Cavalli-Sforza [56]. In 1981, J. Felsenstein [65] fully developed a general ML approach for nucleotide sequence data. The method was also applied on protein data by Kishino in 1990 [109] as well as by Adachi and Hasegawa in 1992 [9]. In addition to the fact that ML is statistically consistent [162], it is also considered to be less error-prone than every other method since it is not considerably affected by errors during the sequencing process.

A ML phylogenetic analysis requires an evolutionary model, that is, a probabilistic model of nucleotide substitution which explains the differences between two sequences. Given a hypothesis  $\Phi$  and observed data  $\Delta$ , the likelihood of the data is given by  $L(\Delta; \Phi) = P(\Delta|\Phi)$ , which is the probability of obtaining  $\Delta$  given  $\Phi$ . Note that the terms 'likelihood' and 'probability' are two distinct concepts when used in a statistical context. Probability represents the odds of observing an unknown outcome based on known input parameters, whereas likelihood is used to predict unknown parameters based on a known outcome. In a phylogenetic context, the unknown hypothesis  $\Phi$  is the phylogenetic tree and the evolutionary model (including the parameters of the model), while the known data  $\Delta$  is the genetic material of the species under investigation (DNA sequences in the input MSA). Thus, the likelihood  $L(\Delta; \Phi)$  of a tree describes how likely it is that the MSA was generated by the specific tree and evolutionary model.

Apart from devising a model of molecular evolution and deploying the likelihood function as optimality criterion to score tree topologies, one more problem remains to be resolved: how to search for the maximum likelihood tree. As pointed out in Section 2.3.2, the number of possible tree topologies grows exponentially with the number of taxa. This makes the creation and evaluation of all possible tree topologies impossible even for a small number of sequences due to prohibitively long execution times. To resolve this issue and make the reconstruction of a phylogeny that comprises hundreds or even thousands of organisms feasible, heuristic approaches are employed to search the tree space. Since heuristic tree-search strategies do not evaluate all possible topologies, the outcome of an analysis is a tree that represents a trade-off between topological accuracy and execution time.

#### 2.4.2.1 Nucleotide substitution models

As already mentioned, a ML analysis relies on a nucleotide substitution model which describes the process of one nucleotide evolving into another. The process of base substitution within a population is generally so slow that it can not be observed during the lifetime of a human being, but a detailed examination of DNA sequences can provide insight on the process. Evolutionary changes in DNA sequences are revealed by comparisons between species that share a common ancestor. These comparisons require the use of statistical methods that make several assumptions about the nucleotide substitution process. These methods usually assume that individual sequence sites have evolved independently of each other. The change from a character state *i* to a character state *j* along a branch of a tree is usually modeled as a continuous-time homogeneous Markov process. The main property of a Markov chain is that it is memoryless. This means that the change from a state *A* to a state *B* depends only on the current state *A*. To put this into an evolutionary context, assume a sequence *s* and the nucleotide base *A* at a position *x* of the sequence at time  $t_0$ . The probability of observing another nucleotide base, *T* for instance, at the same position at some later time  $t_1$  depends only on the fact that an *A* was present at time  $t_0$ .

The mathematical formulation of an evolutionary model is a matrix of base substitution rates. There are 4 possible character states in a nucleotide sequence (A, C, G, T for DNA data and A, C, G, U for RNA data), while there are 20 possible character states (A, C, D, E, F, G, H, I, K, L, M, N, P, Q, R, S, T, V, W, Y) in an amino acid sequence. Thus, the base substitution matrix is of size  $4 \times 4$  when it models nucleotide substitution rates whereas it is of size  $20 \times 20$  when it models amino acid substitution rates. The generic form of the nucleotide substitution matrix is given by Equation 2.4. Each  $Q_{ij}$  element represents the substitution rate from a base *i* to a base *j* in an infinitely small time interval dt.

$$Q = \begin{pmatrix} -\mu(a\pi_{C} + b\pi_{G} + c\pi_{T}) & \mu a\pi_{C} & \mu b\pi_{G} & \mu c\pi_{T} \\ \mu g\pi_{A} & -\mu(g\pi_{A} + d\pi_{G} + e\pi_{T}) & \mu d\pi_{G} & \mu e\pi_{T} \\ \mu h\pi_{A} & \mu j\pi_{C} & -\mu(h\pi_{A} + j\pi_{C} + f\pi_{T}) & \mu f\pi_{T} \\ \mu i\pi_{A} & \mu k\pi_{C} & \mu l\pi_{G} & -\mu(i\pi_{A} + k\pi_{C} + l\pi_{G}) \end{pmatrix}$$

(2.4)

In this matrix, the rows and columns are ordered by the alphabetical order of the bases A, C, G, and T. Parameter  $\mu$  represents the mean instantaneous substitution rate from one nucleotide to another. The parameters a, b, ..., l correspond to every possible transformation between distinct bases. The product of each one of them and the mean instantaneous substitution rate constitutes a rate parameter. Parameter  $\mu$  is usually set to 1, and parameters a, b, ..., l are scaled such that the average substitution rate is 1. Parameters  $\pi_A, \pi_C, \pi_G$ , and  $\pi_T$  are called base frequencies and represent the frequency of occurrence of the bases A, C, G, and T in the input MSA. It is assumed that the nucleotide substitutions are at equilibrium, that is, the proportions of the individual bases remain constant over time. Thus, they also serve as the stationary distribution of the Markov process. The diagonal elements are chosen such that all elements in each row sum up to zero  $(Q_{ii} = -\sum_{i \neq j} Q_{ij})$ , since the rate  $-Q_{ii}$  that the Markov chain leaves state *i* must be equal to the rate  $\sum_{i \neq j} Q_{ij}$  of arriving at all other states together. All models used in real-world analyses are derived from matrix 2.4.

A widely used assumption is that the substitution rate from a base i to a base j in a given period of time  $\Delta t$  is the same as the substitution rate from base j to base i. Evolutionary models that respect this assumption are called *time-reversible* and utilize time-reversible Markov chains. The assumption of time reversibility leads to the following equations for the parameters a, b, ..., l: g = a, h = b, i = c, j = d, k = e and l = f. Applying these equations on matrix 2.4 and setting  $\mu = 1$  leads to the simplified matrix 2.5, which represents the most general form of Q for time reversibility. The evolutionary model described by this matrix is known as the General Time-Reversible (GTR) model [111, 161]. Although there is no biological reason why nucleotide substitution models should be reversible, time-reversibility is mathematically convenient. Furthermore, some of the time-reversible models come close enough to fit real data.

$$Q = \begin{pmatrix} -(a\pi_C + b\pi_G + c\pi_T) & a\pi_C & b\pi_G & c\pi_T \\ a\pi_A & -(g\pi_A + d\pi_G + e\pi_T) & d\pi_G & e\pi_T \\ b\pi_A & d\pi_C & -(h\pi_A + j\pi_C + f\pi_T) & f\pi_T \\ c\pi_A & e\pi_C & f\pi_G & -(c\pi_A + e\pi_C + f\pi_G) \end{pmatrix}$$

(2.5)

Some models impose additional restrictions to the parameters of matrix Q by reducing the number of rate parameters and/or the number of base frequencies. The JC69 [98] model for

instance, proposed by Jukes and Cantor, assumes equal base frequencies ( $\pi_A = \pi_C = \pi_G = \pi_T = 0.25$ ) and rate parameters (a = b = c = d = e = f = g = h = i = j = k = l). Other restricted models are the F81 model by Felsenstein [65] with equal rate parameters and 2 base frequencies, the K2P model by Kimura [108] with 2 rate parameters and equal base frequencies, and the HKY85 model by Hasegawa, Kishino, and Yano [85] with 2 rate parameters and 4 distinct base frequencies. Note that these models are considered as being oversimplified. As a result, the GTR model is predominantly used in modern phylogenetic analyses [160].

Matrix Q provides the substitution rates between bases in an infinitely small time interval dt. However, a substitution probability matrix P is required in order to compute the likelihood of a tree. Each  $p_{ij}$  element in P represents the probability that a base i will evolve into base j after time t. The substitution probability matrix P is computed as shown in Equation 2.6.

$$P(t) = e^{Qt} \tag{2.6}$$

The exponential can be evaluated by decomposition of Q into its eigenvalues and eigenvectors [114]. There exist closed-form analytical solutions for the substitution probability matrices of the simpler models like JC69, K2P, and HKY85 [195]. For the GTR model, the decomposition of Q requires linear algebra approaches (eigenvalue/eigenvector decomposition) [195].

#### 2.4.2.2 Rate heterogeneity

The aforementioned models assume that all sites of the alignment evolve at the same rate. However, there is strong biological evidence for rate variation among sites. Assuming rate homogeneity among sites represents an oversimplification of the actual evolutionary process. Analyzing alignments that comprise several genes for instance, requires not only different substitution rates among the sites but also a different base substitution model for each gene. Several studies [41, 70, 211] have shown that ignoring rate variation among sites in a likelihood-based phylogenetic analysis can lead to erroneous results if the rates vary among the sites.

Rate heterogeneity among alignment sites can be accommodated by using an additional rate parameter  $r_i$  (i = 1, ..., l, with l being the number of alignment sites) to compute the substitution probability matrix P as shown in Equation 2.7.

$$P(t,r_i) = e^{r_i Q t} \tag{2.7}$$

Note that the substitution rate matrix Q is fixed, whereas only parameter r varies from site to site leading to a different substitution probability matrix P per site. G. Olsen developed a software tool (DNArates [145]) that computes a ML estimate of the individual per-site rates for a fixed tree topology. However, employing individual per-site evolutionary rates is not often used in real-world analyses because of statistical concerns regarding over-parameterization and over-fitting of the data [181]. Modern phylogenetic software tools account for rate heterogeneity among sites using either the  $\Gamma$  model [209] of rate heterogeneity or, a memory- and time-efficient approximation for it, the CAT model [181]. The  $\Gamma$  model, proposed by Z. Yang in 1993, allows continuous variability of mutation rates over sites. The  $\Gamma$  density function is

$$g(r;\alpha,\beta) = \frac{\beta^{\alpha} r^{\alpha-1} e^{-\beta r}}{\Gamma(\alpha)}.$$

(2.8)

A mean distribution rate of 1 is obtained by setting the scale parameter  $\beta$  equal to the shape parameter  $\alpha$ , and thus maintain Q's mean substitution rate of 1. The  $\alpha$  parameter is inverse to the coefficient of variation of the substitution rate, that is, a low  $\alpha$  suggests significant rate differences among sites while a high  $\alpha$  means low rate variation. When  $\alpha \to \infty$ , the distribution degenerates into a model of a single rate for all sites.

Z. Yang also proposed the discrete  $\Gamma$  model [210], which approximates the continuous rate distribution by dividing the sites into distinct rate categories. Yang found that the discrete  $\Gamma$  model with 4 discrete rates provides a good approximation and significantly reduces runtime. Consequently, most software tools for phylogenetic inference employ the discrete  $\Gamma$  model with 4 distinct rate categories instead of the continuous  $\Gamma$  model.

#### 2.4.2.3 Phylogenetic likelihood function

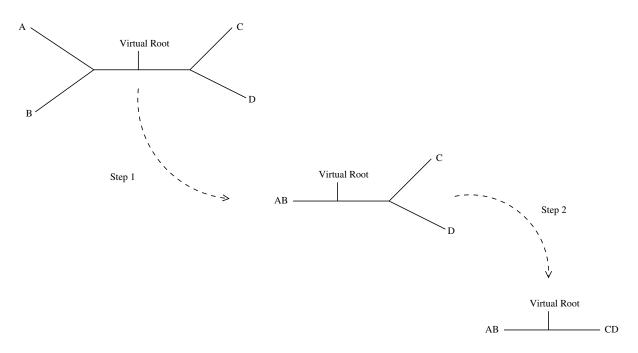

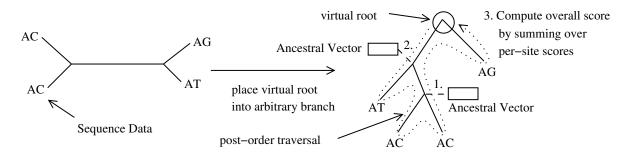

The phylogenetic likelihood function (PLF) computes the likelihood on a given tree topology. All likelihood-based programs deploy the PLF to score trees. The calculation of the PLF is based on two computational techniques, the Felsenstein's pruning algorithm and the Pulley Principle [65], which allow the construction of an iterative procedure for evaluating a fixed/given tree topology. Phylogenetic trees under ML are unrooted for mathematical and computational reasons [65]. According to the Pulley Principle, any branch of an unrooted tree can be regarded as containing the root as long as the Markov process of base substitution is reversible and there are no constraints on the branch lengths. This essentially permits the trivial transformation of an unrooted tree topology into a rooted one by simply placing a *virtual root* into any branch of the unrooted tree. An important feature of the Pulley Principle is that the likelihood score remains the same regardless of where in the tree the *virtual root* is placed. When a *virtual root* has been placed in a tree, the pruning algorithm can be applied from the tips toward the *virtual root* to "prune" the tree and compute the likelihood score. The pruning algorithm is closely related to the peeling algorithm introduced in [59]. Felsenstein gave the name 'pruning algorithm' because every step of the algorithm prunes (removes) two tips from the tree. Figure 2.9 illustrates how a 4-taxon tree topology is pruned according to this algorithm.

The PLF is applied to a fixed rooted tree topology including fixed branch lengths and given model parameters. The nucleotide or amino acid sequences assigned to the tips of the tree are called OTUs (Operational Taxonomic Units), while the inner nodes are called HTUs (Hypothetical Taxonomic Units), since they represent extinct species for which no sequence data are available. The PLF computations start from the tips and proceed, following a postorder tree traversal, toward the *virtual root*. For every alignment site *i*, at each node *k*, the conditional probability  $L_{s_k}^{(k)}(i)$  is calculated, which describes the probability of observing the

Figure 2.9: Pruning steps for a 4-taxon tree according to Felsenstein's pruning algorithm.

data at the descendants of node k given the state  $s_k$  at node k. For the simplest case of applying the PLF on DNA data there are four possible nucleotide states:  $s_k \in \{A, C, G, T\}$ . Thus, a conditional probability vector  $\vec{L}^{(k)}(i)$  (also referred to as likelihood vector) containing four conditional probabilities  $L_{s_k}^{(k)}(i)$  (one for each possible nucleotide state) is computed for the alignment site i of node k:  $\vec{L}^{(k)}(i) = [L_A^{(k)}(i), L_C^{(k)}(i), L_T^{(k)}(i)]$ . The final conditional probability vector  $\vec{L}^{(k)}$  for node k contains m vector entries  $\vec{L}^{(k)}(i)$ , i = 1...m, with m being the number of sites in the MSA. Since all employed base substitution models assume that sites evolve independently (see Section 2.4.2.1), the conditional probabilities  $\vec{L}^{(k)}(i)$  are computed site-by-site by iterating over the MSA alignment columns. In the following, we describe the process of computing the conditional probabilities and the likelihood score for a single site.

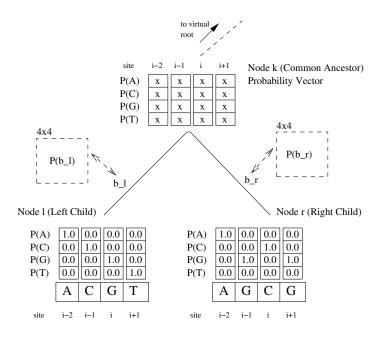

Figure 2.10 provides a schematic representation of a single "pruning" step that removes two tips from the tree. The probabilities at the tips, for which observed data (DNA sequences) is available, are set to 1.0 for the observed nucleotide characters and to 0.0 for all remaining characters at the respective position *i*. For this example, base *G* at position *i* of node *l* (left child) leads to P(G) := 1.0 and P(A) := P(C) := P(T) := 0.0. Apart from the standard nucleotide bases *A*, *C*, *G*, and *T*, there also exist ambiguous characters like *M* for instance, which stands for *A* or *C* and is thus represented by P(A) := 1.0, P(C) := 1.0, P(G) := P(T) := 0.0 at the tip vector level.

A branch length represents the evolutionary time between two nodes in the tree in terms of expected substitutions per site. The branch lengths  $b_l$  and  $b_r$  of the two branches that lead

Figure 2.10: A single pruning step that removes two tips from the tree.

to the left and right child nodes are fixed. Given fixed branch lengths and, therefore, fixed substitution probability matrices  $P(b_l)$  and  $P(b_r)$  (the base substitution model Q is also fixed), the entries of the conditional probability vector at node k are computed as follows:

$$\vec{L}_X^{(k)}(i) = \Big(\sum_{S=A}^T P_{XS}(b_l) \vec{L}_S^{(l)}(i)\Big) \Big(\sum_{S=A}^T P_{XS}(b_r) \vec{L}_S^{(r)}(i)\Big).$$

(2.9)

Equation 2.9 calculates the conditional probability of observing a character X ( $X \in \{A, C, G, T\}$ ) at position *i* of the ancestral node *k* given character states S ( $S \in \{A, C, G, T\}$ ) at the same position *i* of the child nodes *l* and *r*. When the procedure reaches the *virtual root*, Equation 2.9 computes the conditional probability vector  $\vec{L}^{(vr)}$ . The likelihood score of site *i* is computed from the conditional probability vector at the virtual root as follows:

$$l(i) = \sum_{S=A}^{T} \pi_S L_S^{(vr)}(i), \qquad (2.10)$$

where probabilities  $\pi_A$ ,  $\pi_C$ ,  $\pi_G$ , and  $\pi_T$  are the *a priori* probabilities (see Section 2.4.2.1) of observing A, C, G, or T at the *virtual root*. These probabilities can all be set to 0.25, be obtained empirically by counting the occurrences of A, C, G, and T in the MSA, or be estimated using maximum likelihood. The final likelihood score of the tree is the product of all m per-site likelihood scores:

#### 2.4. PHYLOGENETIC INFERENCE METHODS

$$L = \prod_{i=1}^{m} l(i).$$

(2.11)

Note that, because the values in the substitution probability matrices P are  $\leq 1$ , the individual  $L_{s_k}^{(k)}(i)$  values can become very small, thus leading to very small per-site likelihood scores l(i). To prevent numerical underflows, the log likelihood score is usually calculated instead of L:

$$LH = \log(L) = \sum_{i=1}^{m} \log(l(i)).$$

(2.12)

#### 2.4.2.4 Branch length and model parameter optimization

ML analyses aim to reconstruct the phylogenetic tree that maximizes the likelihood score. To obtain the maximum likelihood score for a fixed tree topology, one needs to optimize all branch lengths *and* all model parameters. Both the branch lengths and the model parameters are considered free parameters of the likelihood function.

Model parameter optimization encompasses the estimation of rate parameters in the substitution rate matrix and the parameters that model among-site rate heterogeneity. Substitution models such as HKY85 [85] or GTR [111, 161] assume that branch lengths and model parameters are not correlated. A numerical optimization algorithm [212] that works well in this case typically exhibits two phases. In the first phase, some model parameters can be updated simultaneously using, for instance, the Broyden-Fletcher-Goldfard-Shanno algorithm (BFGS [69, 72]), while branch lengths remain fixed/constant. In the second phase, branch lengths are updated one by one while the model parameters remain fixed. Since model parameter optimization is computationally expensive, model parameters are optimized only crudely in the initial stages of a tree search. When there is a strong correlation between branch lengths and other model parameters, as is the case with the  $\Gamma$  model [209] of rate heterogeneity, the first phase of the algorithm needs to be embedded into the second phase. Therefore, a multivariate optimization algorithm (such as BFGS) can be used to estimate the model parameters while optimizing branch lengths for any given values of the model parameters.

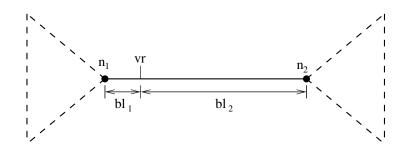

Modern phylogenetic software tools search the tree space via frequent removal and reinsertion of subtrees or related techniques of tree alteration. The branch lengths need to be optimized after each change to the tree topology. The branch lengths of a tree are usually optimized one by one. All other branch lengths except for the one to be optimized are considered to be fixed. Figure 2.11 shows a branch b of length bl that connects two nodes  $n_1$  and  $n_2$ . To optimize this branch, a virtual root is initially placed onto it (Pulley Principle [65], see Section 2.4.2.3). The likelihood score of the tree depends on the distances  $bl_1$  and  $bl_2$  between the virtual root vr and the two nodes  $n_1$  and  $n_2$ . Placing the virtual root right next to node  $n_1$  for instance ( $bl_1 = 0$ ) leads to  $bl = bl_2$ , which allows to optimize the likelihood score of the tree by altering only one parameter ( $bl_2$ ). The Newton-Raphson optimization procedure [156] is often used for this task

Figure 2.11: A branch of a tree to be optimized.

because it has good convergence properties. As with most univariate optimization methods, the first and second partial derivatives of the PLF with respect to the branch length parameter bl need to be calculated.

### 2.4.3 Bayesian inference

Bayesian inference of phylogenies employs the same substitution models (other model parameters) and scoring function as ML inference. In addition, it incorporates prior information about a phylogeny using a prior probability distribution of trees. Felsenstein [63] was the first to suggest the use of Bayesian statistics for reconstructing phylogenies in 1968, but it was not until 1996 that three independent papers [118, 126, 158] showed how posterior probabilities of trees can be calculated under simple priors.

For a number of species s, there exist T(s) alternative tree topologies:  $\tau_1, \tau_2, ..., \tau_{T(s)}$ . Given the observed data  $\Delta$  (the MSA), the posterior probability of observing tree  $\tau_i$  conditional on the data  $\Delta$  is calculated with Bayes's theorem as follows:

$$P(\tau_i|\Delta) = \frac{P(\tau_i)P(\Delta|\tau_i)}{\sum_{j=1}^{T(s)} P(\tau_j)P(\Delta|\tau_j)},$$

(2.13)

where  $P(\tau_i)$  is the prior probability of tree  $\tau_i$ ,  $P(\Delta|\tau_i)$  is the likelihood of tree  $\tau_i$ , and the denominator is a normalizing constant that involves a summation over all T(s) topologies. The likelihood  $P(\Delta|\tau_i)$  is computed by integrating over all possible combinations of branch lengths  $\phi$  and substitution model parameters  $\theta$  as follows:

$$P(\Delta|\tau_i) = \int_{\phi} \int_{\theta} P(\Delta|\tau_i, \phi, \theta) P(\phi, \theta) d\phi d\theta, \qquad (2.14)$$

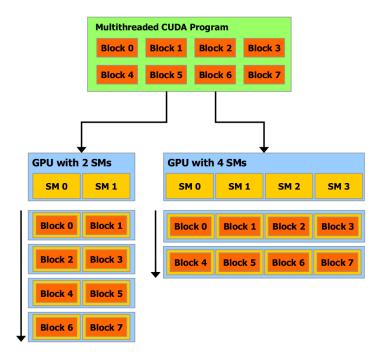

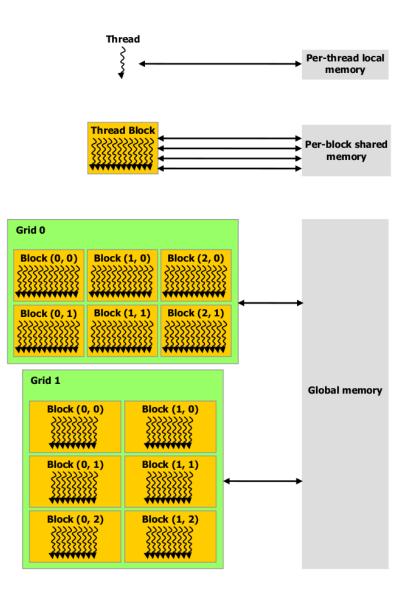

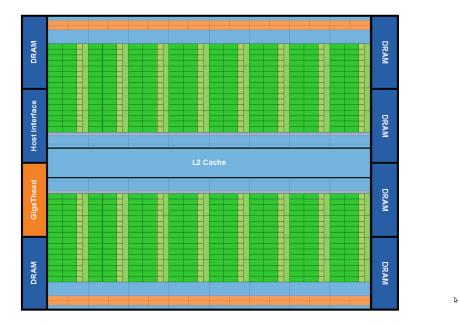

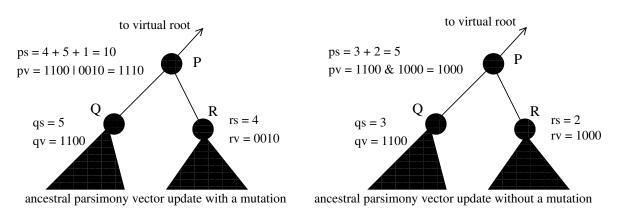

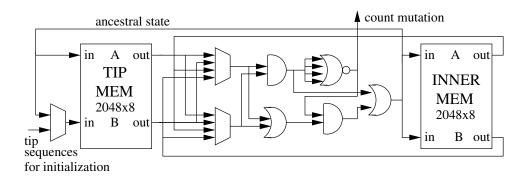

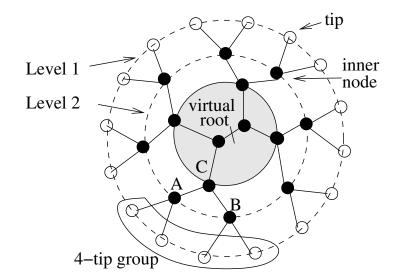

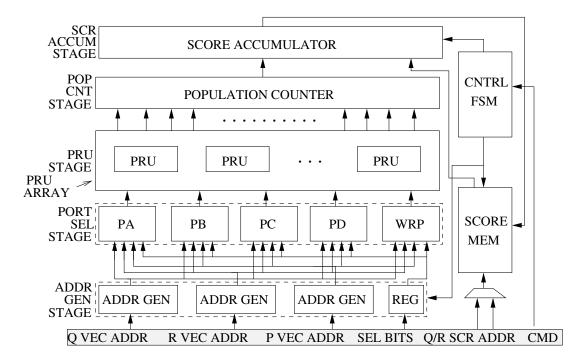

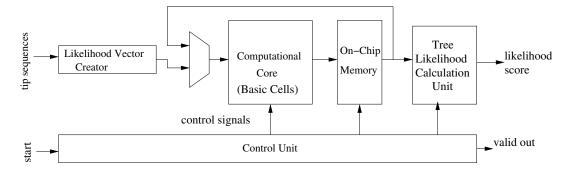

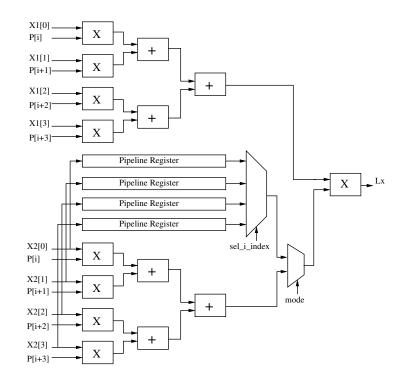

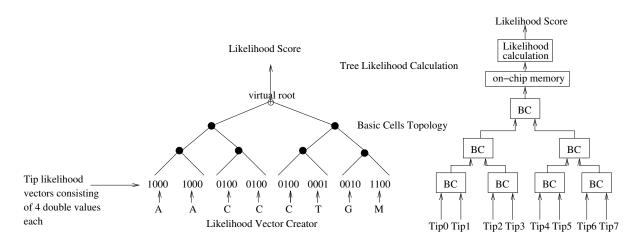

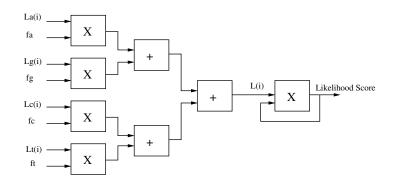

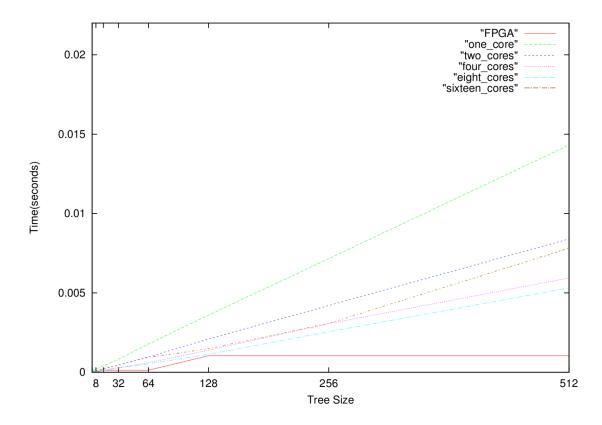

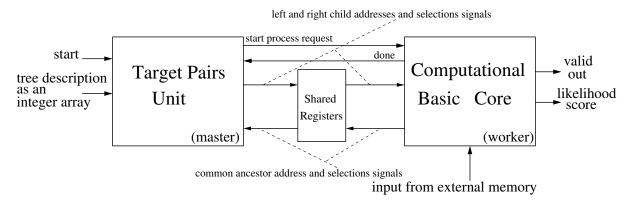

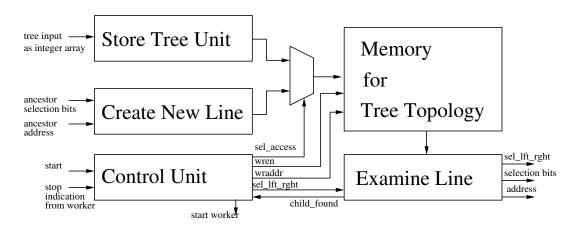

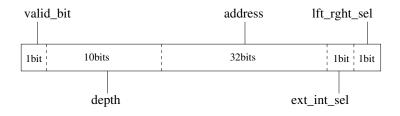

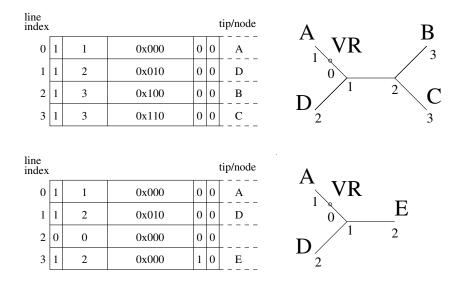

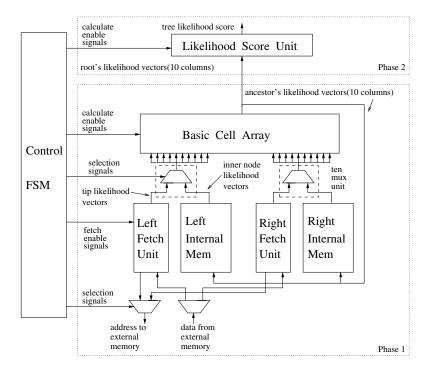

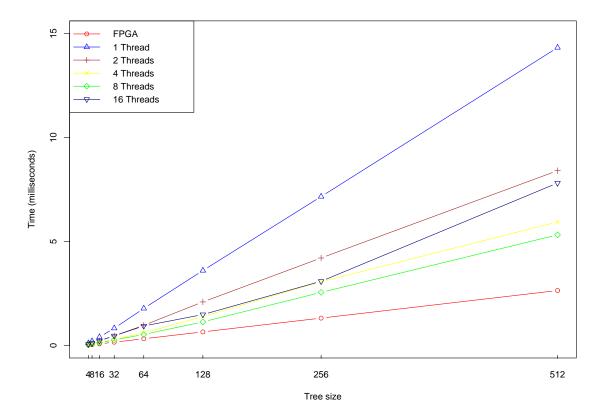

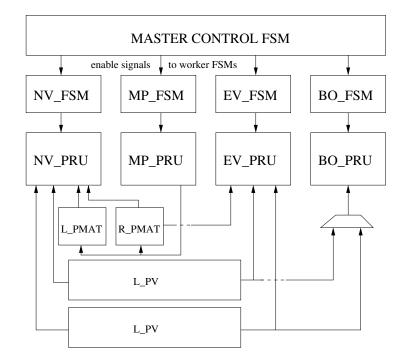

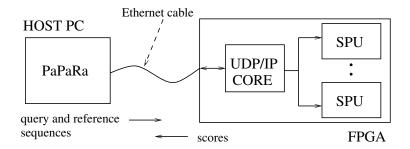

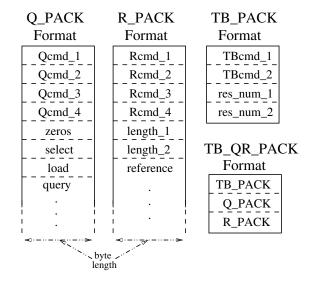

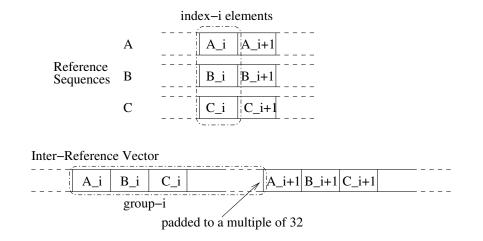

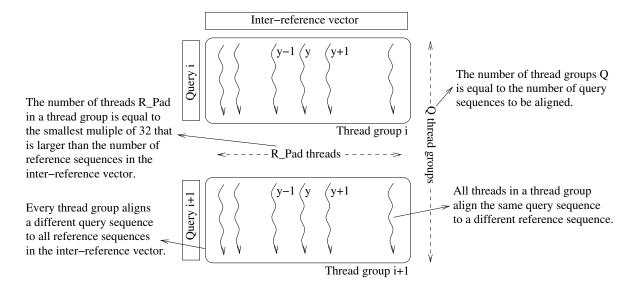

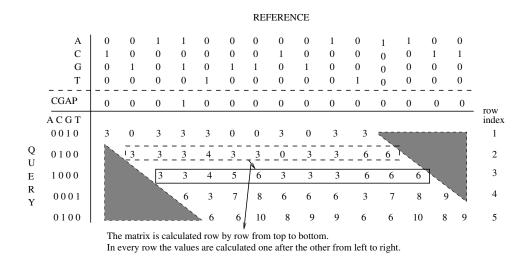

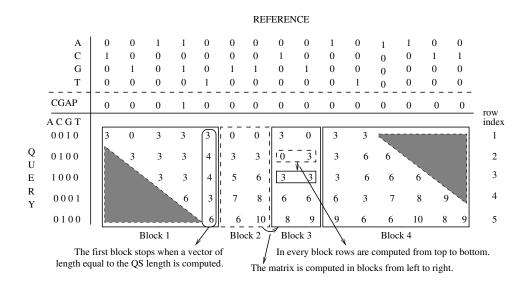

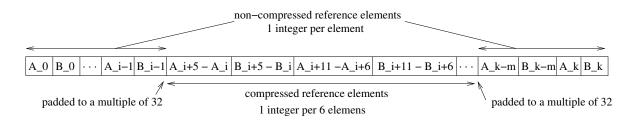

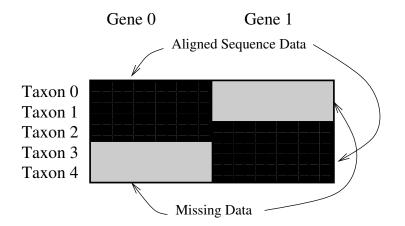

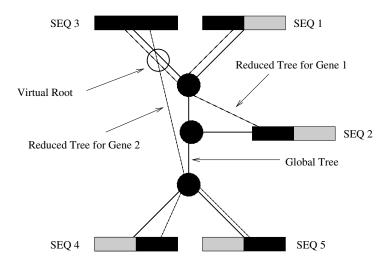

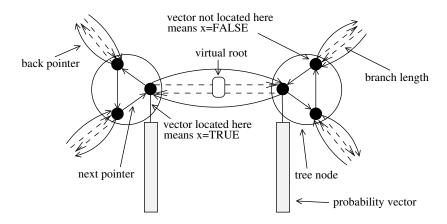

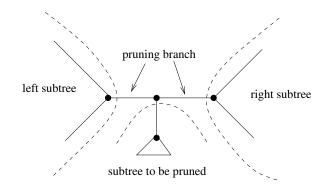

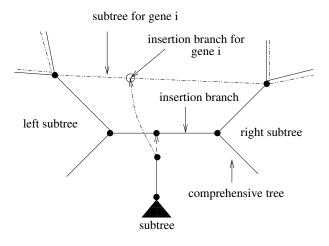

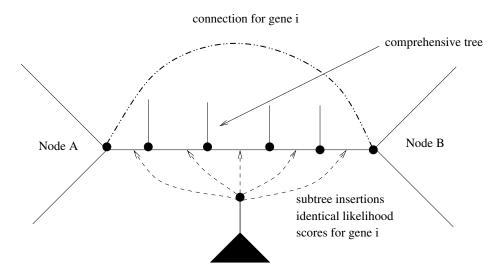

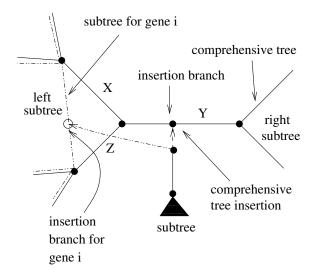

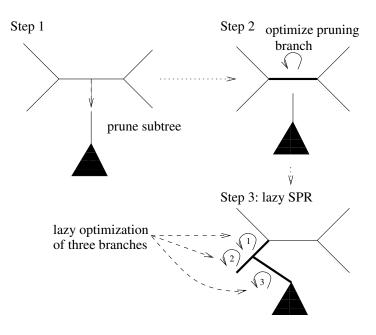

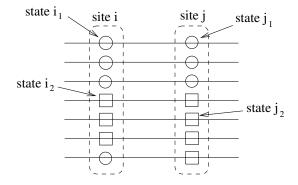

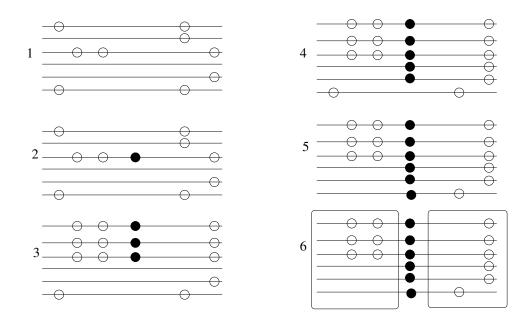

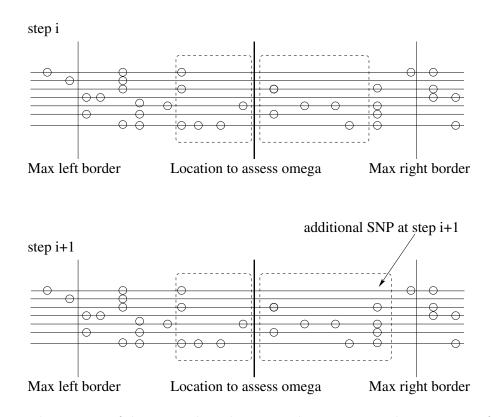

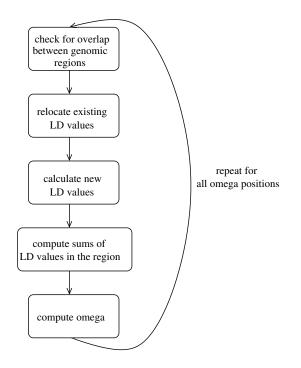

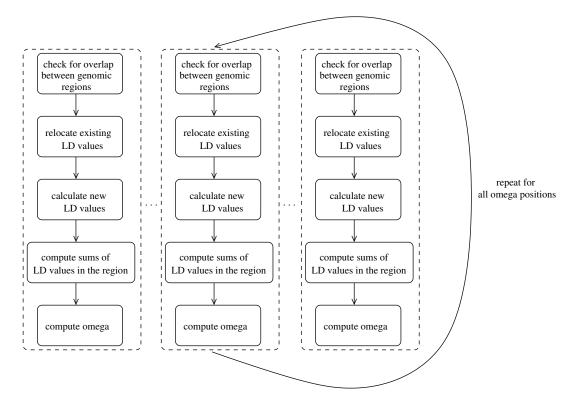

where  $P(\Delta|\tau_i, \phi, \theta)$  can be computed by means of the PLF and  $P(\phi, \theta)$  is the prior probability density of the branch lengths and substitution model parameters.